集成电路可靠性设计 从理念到实践的全面解析

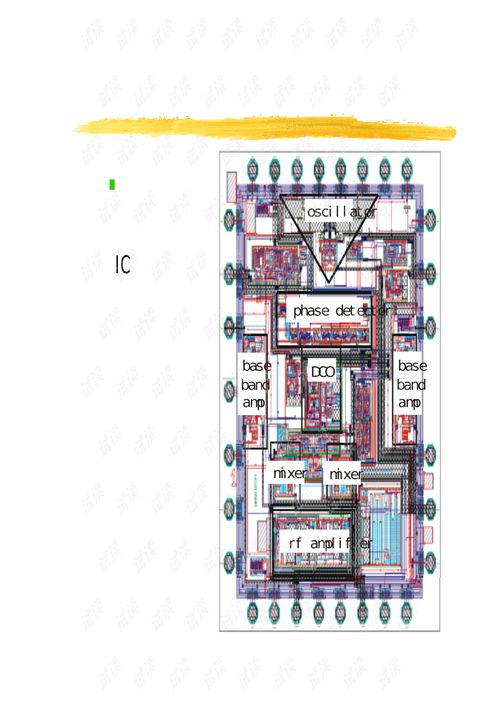

在现代电子工业中,集成电路(IC)作为信息技术的核心基石,其性能与可靠性直接决定了电子设备的稳定性和寿命。随着工艺节点的不断缩小、芯片集成度的持续飙升以及应用场景的日益严苛(如汽车电子、工业控制、航空航天等),传统的设计-制造-测试模式已不足以应对复杂系统的可靠性挑战。因此,可靠性设计已成为集成电路设计流程中不可或缺、甚至需要前置的关键环节。它并非单一技术,而是一套贯穿芯片整个生命周期的系统性方法论,旨在从设计源头预防、控制并缓解失效风险。

一、可靠性设计的核心理念与重要性

可靠性设计的核心目标是确保芯片在其规定的寿命周期内,在预期的使用环境和工作条件下,能够稳定、无误地执行预定功能。它与功能设计、性能设计、功耗设计并列为芯片设计的四大支柱。其重要性体现在:

- 经济性与市场竞争力:早期发现并解决可靠性问题,能极大降低后期测试、返工、维修乃至召回的成本。一颗高可靠的芯片是赢得高端市场(如车规级、军工级)信任的通行证。

- 系统安全与法律责任:在自动驾驶、医疗设备等安全攸关领域,芯片的微小失效可能导致灾难性后果,并带来严峻的法律责任。

- 技术发展的必然要求:先进工艺(如FinFET、GAA)在带来性能提升的也引入了新的可靠性威胁(如栅氧经时击穿、热载流子注入、负偏压温度不稳定性等),必须在设计阶段加以应对。

二、主要可靠性失效机理与设计应对策略

可靠性设计需针对特定的物理失效机理,采取相应的设计加固措施:

- 电迁移:在高电流密度下,金属互连线中的原子被电子“吹走”,导致导线开路或短路。

- 设计策略:遵守更严格的布线规则,使用更宽的导线,增加通孔/接触孔数量,采用铜互连及阻挡层材料,在电路设计中避免持续大电流路径。

- 热载流子注入:高电场下的载流子获得足够能量注入栅氧化层,造成器件参数(如阈值电压)漂移。

- 设计策略:优化器件尺寸和偏置电压,避免晶体管工作在接近击穿电压的区域;采用抗HCI的器件结构或工艺。

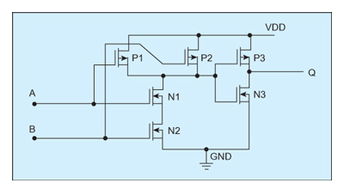

- 负偏压温度不稳定性:主要在PMOS管中,在负栅压和高温下,界面陷阱产生导致阈值电压绝对值升高,驱动能力下降。

- 设计策略:优化工艺以改善栅氧界面质量;在电路设计时考虑NBTI导致的性能退化余量(设计裕度);采用动态偏置或恢复技术。

- 经时击穿:栅氧化层在长期电场应力下累积损伤,最终导致绝缘失效。

- 设计策略:使用更厚或更高质量的栅氧(在性能与可靠性间权衡);严格控制工作电压;采用电压域设计和电源管理技术。

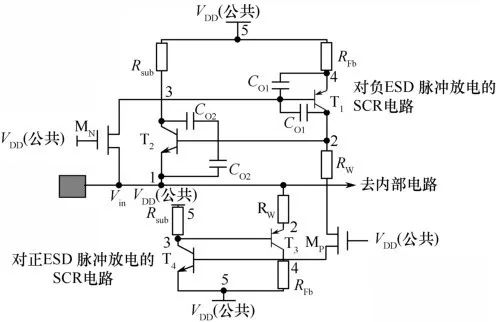

- 静电放电与闩锁效应:外部静电或内部噪声可能引发瞬间大电流,损坏电路或触发寄生可控硅结构导致闩锁。

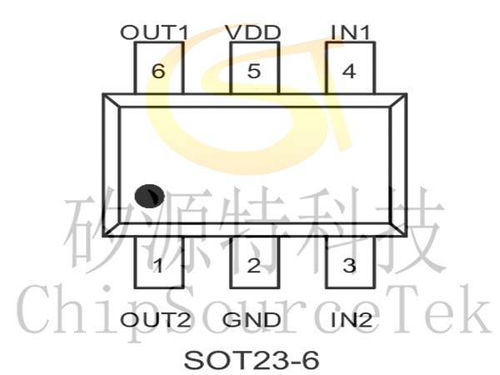

- 设计策略:在芯片所有I/O端口及敏感内部节点设计完整的ESD保护电路(如GGNMOS、RC触发SCR等);通过良好的版图布局(增加保护环、增大间距)来抑制闩锁效应。

- 软错误:由高能粒子(如阿尔法粒子、中子)撞击引发,导致存储单元状态翻转或组合逻辑瞬时错误。

- 设计策略:对关键存储器采用纠错码(ECC)、奇偶校验;对触发器采用加固单元(如DICE单元);系统级采用三模冗余等容错设计。

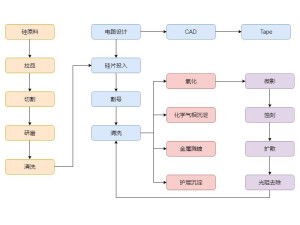

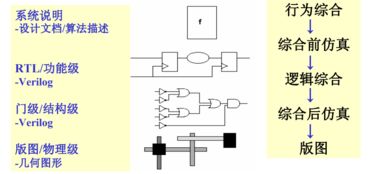

三、可靠性设计流程与方法学

一个系统的可靠性设计流程应融入标准的设计周期:

- 可靠性目标与规范制定:根据产品应用场景(消费级、工业级、车规级),明确具体的可靠性指标(如FIT率、工作寿命、环境耐受等级)。

- 设计阶段的分析与加固:

- 可靠性仿真与预测:使用专用EDA工具,在电路仿真阶段就模拟电迁移、HCI、NBTI等效应,预测电路寿命和参数漂移。

- 设计裕度:在时序、功耗、驱动能力等方面预留足够余量,以抵消老化带来的性能衰减。

- 容错与自修复设计:对于极高可靠要求的系统,采用冗余设计、自检电路、可重构逻辑等。

- 可测试性设计:集成用于监测老化、温度和电压的传感器,以及用于测试内部可靠性的专用电路(如BIST)。

- 版图阶段的可靠性考量:

- 遵守可靠性设计规则:比基础DRC更严格的间距、宽度规则,以应对电迁移和自热效应。

- 均匀性与对称性:确保电源/地网络分布均匀,避免热点;差分对等关键电路严格对称。

- 抗干扰布局:模拟与数字电路隔离,敏感信号屏蔽。

- 验证与评估:

- 可靠性专项验证:检查ESD保护网络、闩锁防护是否完整。

- 老化仿真与寿命评估:通过仿真数据,结合工艺模型,给出芯片的预计寿命。

- 制造、测试与监控:与制造厂合作,监控工艺波动对可靠性的影响;进行加速寿命测试,收集实际数据以校准模型。

四、挑战与未来趋势

面向集成电路可靠性设计面临诸多挑战:

- 先进工艺的复杂性:3D集成、异质集成、原子级尺度器件带来新的、耦合的失效机理。

- 新材料的引入:高k金属栅、二维材料、新型互连材料的可靠性数据库和模型尚不完善。

- 系统级复杂性:芯片-封装-系统协同设计与协同失效分析难度激增。

未来趋势将聚焦于:

- 设计-工艺协同优化:更早、更紧密地与制造端合作。

- 基于机器学习的预测:利用大数据和AI技术,更精准地预测芯片寿命和失效点。

- 智能自愈与自适应系统:芯片能够实时监测自身健康状态,并动态调整工作点或启用备份资源。

- 可靠性标准与IP化:形成更完善的可靠性设计标准库和可复用的可靠性IP,提升设计效率。

###

总而言之,集成电路可靠性设计是一个多学科交叉、贯穿始终的复杂工程。它要求设计师不仅精通电路与系统知识,还需深刻理解半导体物理、材料科学和失效机理。在“后摩尔时代”,当纯粹的性能提升愈发困难,可靠性将成为衡量芯片价值和竞争力的最关键维度之一。从设计伊始就将可靠性内植于芯片基因,是打造成功产品、赢得长远市场的必由之路。

如若转载,请注明出处:http://www.yehongjy.com/product/69.html

更新时间:2026-02-24 12:54:09