探索微世界 集成电路设计的奥秘与未来

集成电路(Integrated Circuit,简称IC)设计是现代电子工业的核心与基石,它不仅是技术创新的驱动力,也是信息时代得以蓬勃发展的关键所在。从智能手机、个人电脑到数据中心、人工智能系统,乃至汽车电子和物联网设备,几乎每一个现代科技产品都依赖于复杂而精密的集成电路。本文将深入探讨IC设计的基本概念、主要流程、关键技术挑战以及未来发展趋势。

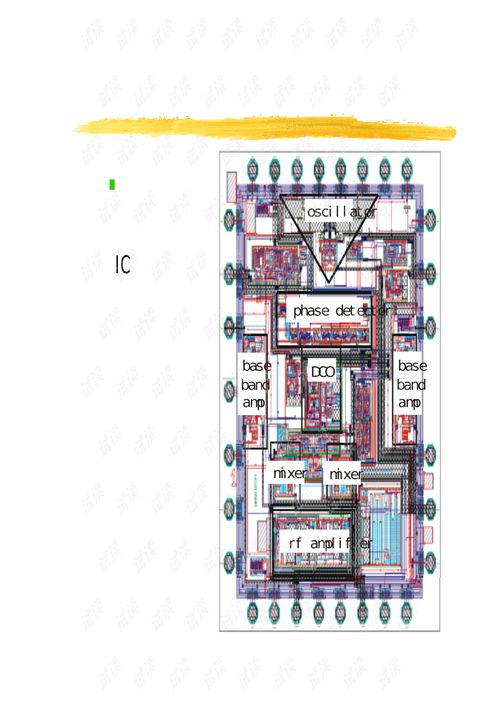

一、IC设计的基本概念

IC设计,简单来说,就是在一块微小的半导体材料(通常是硅)上,通过一系列复杂的物理和化学过程,将数以亿计的晶体管、电阻、电容等电子元件以及它们之间的互连线集成在一起,形成一个具有特定功能的电路系统。这个过程就像是建造一座微型的、功能齐全的“电子城市”。根据电路功能的复杂度和设计方法的不同,IC主要可以分为模拟集成电路、数字集成电路和混合信号集成电路三大类。

二、IC设计的主要流程

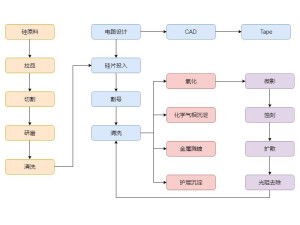

一个完整的IC设计流程是一个高度系统化、多阶段的工程过程,通常可以分为以下几个关键步骤:

- 规格定义与系统架构设计:这是设计的起点。工程师需要明确芯片需要实现的功能、性能指标(如速度、功耗、面积)、工作环境以及目标成本。在此基础上,进行高层次系统架构的规划与模块划分。

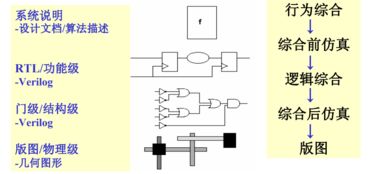

- 前端设计(逻辑设计):使用硬件描述语言(如Verilog或VHDL)对芯片的寄存器传输级(RTL)行为进行建模和描述。这一阶段主要关注功能的正确性,通过仿真验证逻辑是否符合规格要求。

- 功能验证:这是确保设计正确的关键环节。通过搭建复杂的测试平台,运用仿真、形式验证等多种手段,对RTL设计进行 exhaustive 的测试,以发现并修复逻辑错误。验证工作通常占整个设计周期的一半以上。

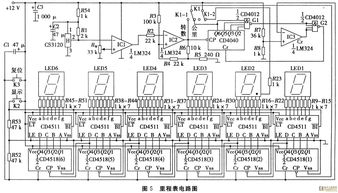

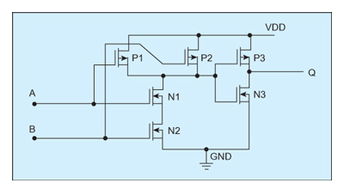

- 逻辑综合:将RTL代码通过电子设计自动化(EDA)工具,转换成由标准单元库(如与门、或门、触发器等)构成的网表。综合过程会优化电路的面积、时序和功耗。

- 后端设计(物理设计):这是将逻辑网表转化为实际物理版图的过程。主要包括布局(决定每个标准单元在芯片上的位置)、布线(连接各个单元)、时钟树综合(构建全局时钟网络)和物理验证(检查设计规则、电气规则等是否符合芯片制造厂的要求)。

- 流片与测试:将最终确认的版图数据(GDSII格式)交付给晶圆代工厂进行制造,这个过程称为“流片”。芯片制造出来后,需要进行严格的封装和测试,以确保其功能和性能达标。

三、关键技术挑战

随着摩尔定律的持续推进,IC设计面临着前所未有的挑战:

- 设计复杂性爆炸:数十亿晶体管的集成使得设计、验证和测试的复杂度呈指数级增长。

- 功耗墙:性能提升的功耗密度急剧增加,散热和能效成为核心瓶颈。

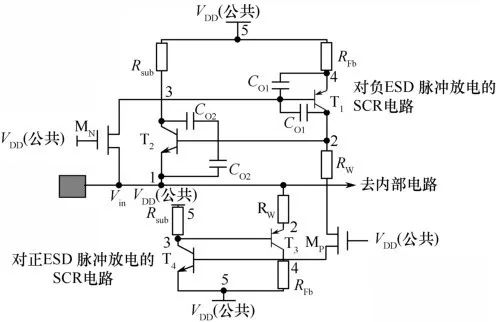

- 时序收敛与信号完整性:在纳米甚至更小工艺下,互连线延迟、串扰、电源噪声等问题日益突出。

- 制造成本飙升:先进工艺节点的研发和建厂成本极高,使得只有少数巨头能够参与竞争。

- 人才短缺:培养一名经验丰富的IC设计工程师需要漫长的周期,全球范围内高端人才供不应求。

为了应对这些挑战,业界正在大力发展新的设计方法学和工具,如基于高级综合(HLS)的设计、异构集成(Chiplet)、硅光子学、以及广泛利用人工智能(AI)技术进行设计空间探索、布局布线和缺陷检测。

四、未来发展趋势

IC设计将朝着以下几个方向演进:

- 超越摩尔(More than Moore):在继续追求晶体管微缩的更注重通过系统级封装(SiP)、Chiplet(芯粒)等异构集成技术,将不同工艺、不同功能的芯片模块集成在一起,实现更高的系统性能与灵活性。

- 专用领域架构(DSA)的兴起:针对人工智能、自动驾驶、5G通信等特定应用场景,设计高度定制化、能效比极佳的专用芯片,正成为主流趋势,打破了通用处理器(CPU)的垄断。

- EDA与AI的深度融合:人工智能将深度赋能IC设计的各个环节,从架构探索、代码生成到物理实现和验证,大幅提升设计自动化水平和效率,降低对资深工程师经验的依赖。

- 开源生态的构建:类似于开源软件,开源硬件(如RISC-V指令集架构)和开源EDA工具链正在兴起,旨在降低设计门槛,促进创新,构建更健康、多元的产业生态。

- 新材料与新器件:碳纳米管、二维材料(如石墨烯)、自旋电子器件等有望在未来颠覆传统的硅基CMOS技术,开启全新的计算范式。

###

集成电路设计是一门融合了电子工程、计算机科学、物理学和材料科学的尖端交叉学科。它既是一门严谨的工程科学,也是一门充满创造力的艺术。在数字化、智能化浪潮席卷全球的今天,IC设计的重要性愈发凸显。它不仅关乎国家科技竞争力和产业安全,更是在微观尺度上塑造我们未来生活面貌的核心力量。面对挑战,拥抱变化,持续创新,是IC设计领域永恒的主题。

如若转载,请注明出处:http://www.yehongjy.com/product/65.html

更新时间:2026-02-24 20:02:32