集成电路设计中的防DPA攻击方法

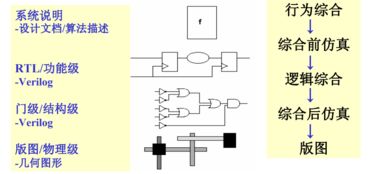

随着集成电路在安全关键领域(如金融、通信、国防)的广泛应用,其面临的安全威胁日益严峻。差分功耗分析(DPA)攻击作为一种高效的侧信道攻击手段,能够通过分析设备运行时的功耗变化来提取密钥等敏感信息,对芯片安全构成了严重威胁。因此,在集成电路设计阶段融入防DPA攻击的防护措施,已成为安全芯片设计的核心环节。

防DPA攻击的集成电路设计方法主要从降低功耗与信息泄露的相关性、增加噪声干扰以及采用安全的算法与架构三个层面展开。

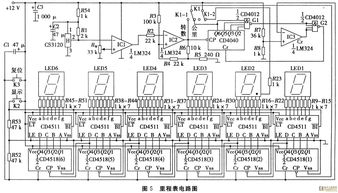

1. 电路级防护:平衡功耗与随机化

在电路级,核心思路是消除或削弱功耗与所处理数据、操作之间的依赖关系。

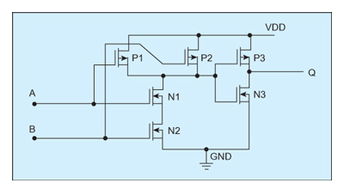

- 功耗平衡逻辑:采用双轨预充逻辑(如WDDL)等技术,使电路无论处理“0”还是“1”,其充放电活动与功耗都尽可能保持一致,从而使得功耗轨迹不泄露数据信息。

- 随机化与掩码技术:通过在数据路径上引入随机掩码,将真实的中间值与随机数进行组合运算,使得功耗特征随机化。攻击者难以从混乱的功耗曲线中提取有效信息。这需要在算法、架构和电路层面协同设计,确保掩码在运算全程有效且最终能被安全移除。

- 异步电路设计:异步电路没有全局时钟,其功耗在时间上分布更均匀,不易产生与时钟同步的、规律性的功耗峰值,从而增加了DPA攻击的难度。

2. 系统级防护:噪声注入与动态调节

在更高的系统层级,通过主动控制来干扰攻击者的测量与分析。

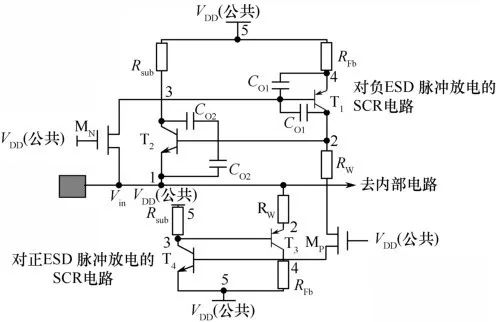

- 内部噪声发生器:在芯片内部集成随机噪声源(如真随机数发生器TRNG),并主动将其注入电源网络或时钟网络中,从而“淹没”与操作相关的细微功耗信号。

- 动态频率与电压调节:动态地改变芯片的工作频率和核心电压,使得功耗曲线的时序和幅度发生不可预测的变化,破坏DPA攻击所需的多次测量间的对齐性。

- 功耗均衡调度:通过调度器,让高功耗操作和低功耗操作交错执行,或者让不相关的模块同时运行,使得整体功耗轮廓趋于平坦。

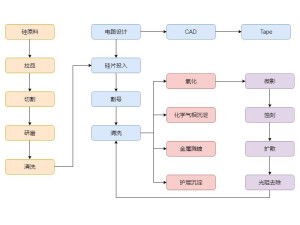

3. 算法与架构级防护

这是最根本的防护层,旨在从计算本身降低信息泄露。

- 抗侧信道攻击的密码算法实现:在实现AES、RSA等密码算法时,采用诸如掩码、隐藏等安全实现方式,确保即使功耗被采集,其与密钥的关联性也极低。

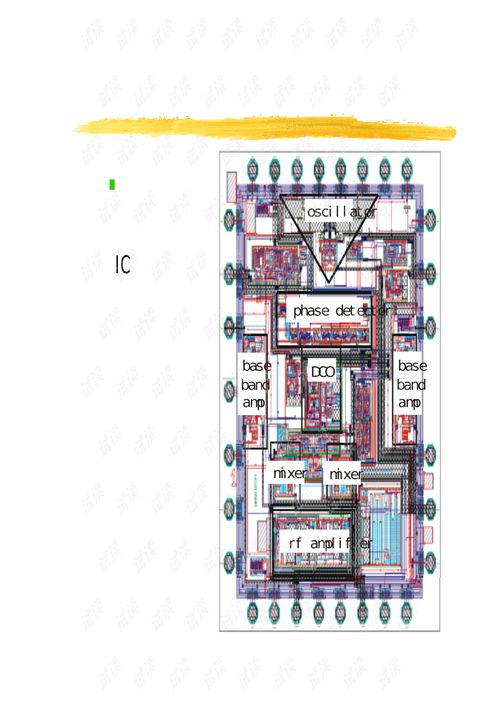

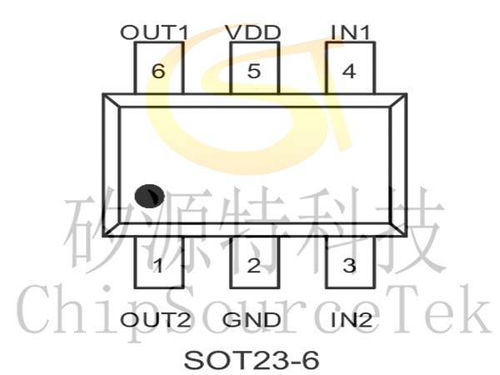

- 安全隔离与分区:采用多核、TrustZone等硬件安全架构,将敏感计算与普通操作在物理或逻辑上隔离,限制攻击者可观测的功耗范围。

- 传感器与主动防御:集成温度、电压、频率传感器,用于检测异常工作条件(可能预示着攻击行为),并触发重置、擦除密钥等主动防御机制。

设计挑战与权衡

实施上述防护方法并非没有代价。功耗平衡逻辑会显著增加芯片面积和功耗;随机化技术可能降低运算速度并增加设计复杂性;噪声注入本身也消耗能量。因此,集成电路安全设计是一个多维度的权衡过程,需要在安全性、性能(速度、功耗)、面积(成本)之间找到最佳平衡点。

结论

防御DPA攻击需要一种贯穿集成电路设计全流程的、分层的安全设计理念。单一的防护措施难以应对所有攻击变种,因此必须结合电路级、系统级和算法架构级的多种技术,构建纵深防御体系。随着攻击技术的不断演进,防DPA攻击的设计方法也需持续创新与改进,通过系统性的防护策略,在芯片的根源上筑牢安全防线,确保敏感信息即使在物理可触及的环境下也能得到有效保护。

如若转载,请注明出处:http://www.yehongjy.com/product/68.html

更新时间:2026-02-24 15:38:30